Simulazione ed uso di GTKWave

Documentiamo qui il software da utilizzare per il testing e debugging delle reti prodotte, ossia iverilog, vvp e GTKWave.

A differenza dell'ambiente per Assembler, questi sono facilmente reperibili per ogni piattaforma, o compilabili dal sorgente.

In sede d'esame si utilizzano da un normale terminale Windows, senza utilizzare macchine virtuali.

Qui si trovano installer per Windows.

Negli esercizi di esame vengono forniti i file necessari a compilare simulazioni per testare la propria rete.

Questi sono tipicamente i file testbench.v e reti_standard.v.

Il primo contiene una serie di test che verificano il corretto comportamento della rete prodotta rispetto alle specifiche richieste.

Il secondo contiene invece delle reti combinatorie che si potranno assumere note e sintetizzabili, da usare per la sintesi di rete combinatoria.

Non tutti gli esercizi hanno una parte di sintesi di rete combinatoria, e quindi il file reti_standard.v.

Inoltre, ciascun esercizio ha il proprio file reti_standard.v, che sarà diverso da quelli allegati ad altri esercizi.

Compilazione e simulazione

Sia descrizione.v il sorgente contenente la descrizione della rete sincronizzata da noi prodotto, e che vogliamo testare.

Si compila la simulazione con il comando da terminale iverilog.

Il comando richiede come argomenti i file da compilare assieme.

Di default, il binario prodotto si chiamerà a.out, mentre con l'opzione -o nome è possibile impostarne uno a scelta.

Per esempio:

iverilog -o desc testbench.v reti_standard.v descrizione.v

Il file prodotto non è eseguibile da solo, ma va lanciato usando vvp.

Per esempio:

vvp desc

Questo lancerà la simulazione. In un test di successo, vedremo le seguenti stampe:

VCD info: dumpfile waveform.vcd opened for output.

$finish called at [un numero]

La prima stampa ci informa che il file waveform.vcd sta venendo popolato, la seconda ci informa del tempo di simulazione al quale questa è terminata con il comando $finish.

Alcune versioni di vvp non stampano quest'ultima di default - non è un problema.

Le testbench degli esercizi d'esame stampano a video quando incontrano un errore: un test fallito avrà quindi delle righe in più in mezzo a quelle presentate qui.

Per esempio, Timeout - waiting for signal failed indica che la simulazione si era bloccata in attesa di un evento che non è mai accaduto, come un segnale di handshake.

Se la simulazione non stampa errori, questo indica solo che la testbench non ne ha trovato alcuno. Non implica, invece, che non ci siano errori. Questo sia perché è impossibile scrivere una testbench davvero esaustiva per tutti i possibili percorsi di esecuzione, ma anche perché è facile scrivere Verilog che sembra funzionare bene ma che in realtà usa costrutti che rendono la rete irrealizzabile in hardware.

È sempre responsabilità dello studente assicurarsi che non ci siano errori. In fase di autocorrezione, anche se la testbench non trova nessun errore, è sempre possibile (anzi, dovuto) assicurarsi della correttezza del compito e fare correzioni se necessarie.

Testbench con `timescale

Con la sintassi `timescale è possibile controllare l'unità di misura default e la granularità della simulazione.

Per esempio, un file testbench.v che comincia come segue imposta l'unità di misura a 1s (il solito) e la granularità di simulazione a 1ms, permettendo di osservare cambiamenti più veloci di un secondo.

`timescale 1s/ms

module testbench();

...

Questa sintassi è utilizzata in alcuni testi d'esame, per esempio se sono previste RC particolarmente veloci. Per maggiori dettagli, vedere qui.

Se la sintassi `timescale è utilizzata, è obbligatorio compilare la simulazione ponendo il file testbench.v come primo file del comando, ossia iverilog -o desc testbench.v ....

In caso contrario, il compilatore stamperà il seguente warning:

warning: Found both default and `timescale based delays.

Waveform e debugging

La simulazione genera un file waveform.vcd contenente l'evoluzione di tutti i fili e registri nella simulazione.

Questo file è prodotto grazie alle seguenti righe, incluse in tutte le testbench:

initial begin

$dumpfile("waveform.vcd");

$dumpvars;

...

Con questo file possiamo studiare l'evoluzione della rete e trovare eventuali errori. Per analizzarlo, usiamo GTKWave, richiamabile da terminale con

gtkwave waveform.vcd

Si dovrebbe aprire quindi una finestra dal quale possiamo analizzare l'evoluzione della rete.

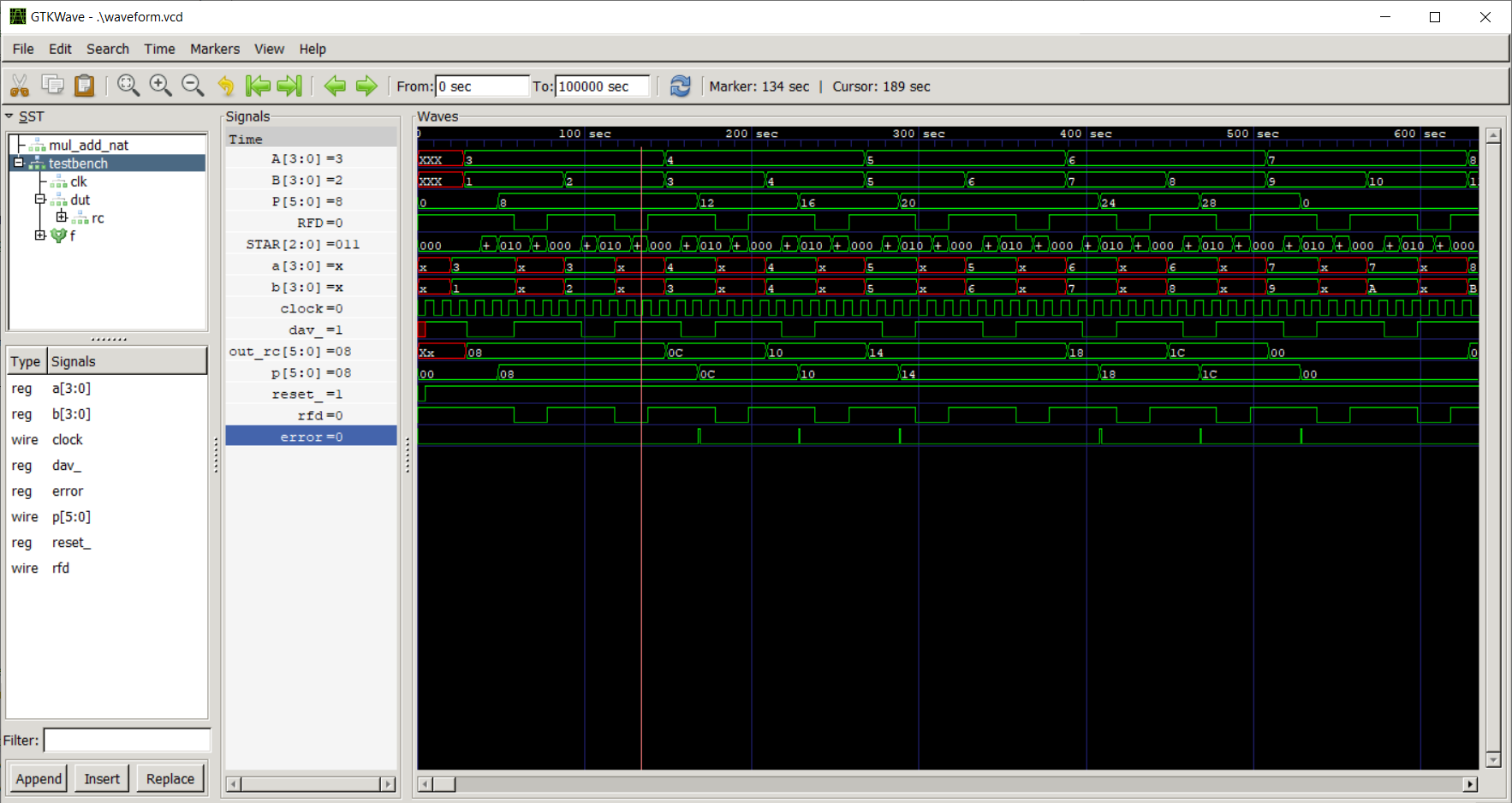

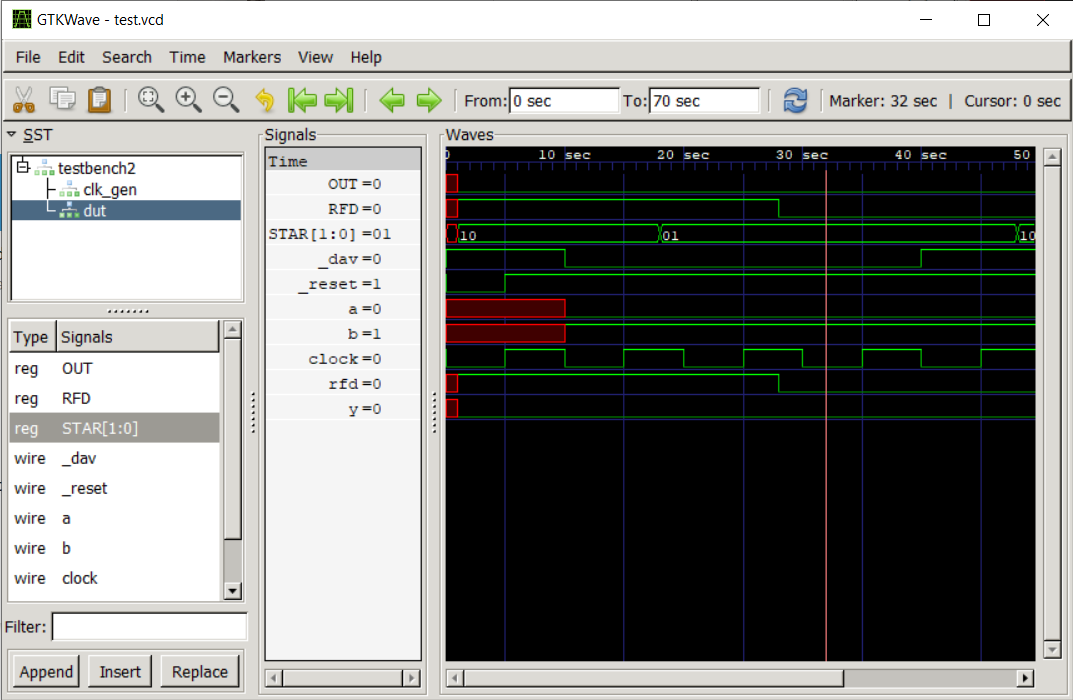

Il programma mostra sulla sinistra le varie componenti nella simulazione e, se li selezioniamo, i fili e registri che li compongono.

Ci interesserà in particolare dut (device under test), che sarà proprio il componente da noi realizzato.

Selezionando poi i vari wire e reg che compaiono sotto, e cliccando "Append", compariranno nella schermata a destra, dove possiamo vedere l'evoluzione nel tempo.

Zoom, ordinamento, formattazione

Lo zoom della timeline a destra è regolabile, usando la rotellina del mouse o le lenti d'ingrandimento in alto a sinistra.

Cliccando in punti specifici della timeline spostiamo il cursore, cioè la linea rossa verticale. Possiamo quindi leggere nella colonna centrale il valore di ciascun segnale all'istante dove si trova il cursore.

I segnali nella schermata principale sono ordinabili, per esempio è in genere utile spostare clock e STAR in alto.

Di default, sono formattati come segnali binari, se composti da un bit, o in notazione esadecimale, se da più bit.

Cliccando col destro su un segnale è possibile cambiare la formattazione in diversi modi, incluso decimale.

Non specificati e alta impedenza

Prestare particolare attenzione ai valori non specificati (X) e alta impedenza (Z), che sono spesso sintomi di errori, per esempio per un filo di input non collegato.

Nella waveform, i valori non specificati sono evidenziati con un'area rossa, mentre i fili in alta impedenza sono evidenziati con una linea orizzontale gialla posta a metà altezza tra 0 e 1.

Pulsante Reload

Il comando gtkwave waveform.vcd blocca il terminale da cui viene lanciato, rendendo impossibile mandare altri comandi finché non viene chiuso.

È quindi frequente vedere studenti chiudere e riaprire GTKWave ogni volta che c'è bisogno di risimulare la rete.

Questo approaccio è però inefficiente, dato che si dovrà ogni volta riselezionare i fili, riformattarne i valori, ritrovare il punto d'errore che si stava studiando.

Il pulsante Reload, indicato con l'icona 🔁, permette di ricaricare il file waveform.vcd senza chiudere e riaprire il programma, e mantentendo tutte le selezioni fatte.

È per questo una buona idea utilizzare una delle seguenti strategie:

- usare due terminali, uno dedicato a

iverilogevvp, l'altro agtkwave; - lanciare il comando

gtkwavein background. Nell'ambiente Windows all'esame, questo si può fare aggiungendo un&in fondo:gtkwave waveform.vcd &.

In entrambi i casi, otteniamo di poter rieseguire la simulazione mentre GTKWave è aperto, e poter quindi sfruttare il pulsante Reload.

& non funzionaIn alcune installazioni di Powershell l'operatore & non funziona.

L'operatore è un semplice alias per Start-Job, e si può ovviare al problema usando questo comando per esteso:

Start-Job { gtkwave waveform.vcd }

L'operatore è documentato qui.

Linea di errore

Nelle testbench d'esame è (di solito) presente anche una linea di errore che permette di identificare subito i punti in cui la testbench ha trovato un errore. Questo è particolarmente utile per scorrere lunghe simulazioni.

Queste linee sono realizzate nella testbench con una variabile reg error inizializzata a 0 e un blocco always che risponde ad ogni variazione di error per rimetterla a 0 dopo una breve attesa.

Questa attesa breve ma non nulla fa sì che basti assegnare 1 ad error per ottenere un'impulso sulla linea, facilmente visibile.

In GTKWave, possiamo trovare il segnale error tra i wire e reg del modulo testbench (non in dut).

Mostrando questo segnale, possiamo riconoscere i punti di errore come impulsi, come nell'esempio seguente.